PDF) Vlsi Design of Low Transition Low Power Test Pattern Generator Using Fault Coverage Circuits | IOSR Journals - Academia.edu

PDF) Power Reduction Technique in LFSR using Modified Control Logic for VLSI Circuit | praveen j - Academia.edu

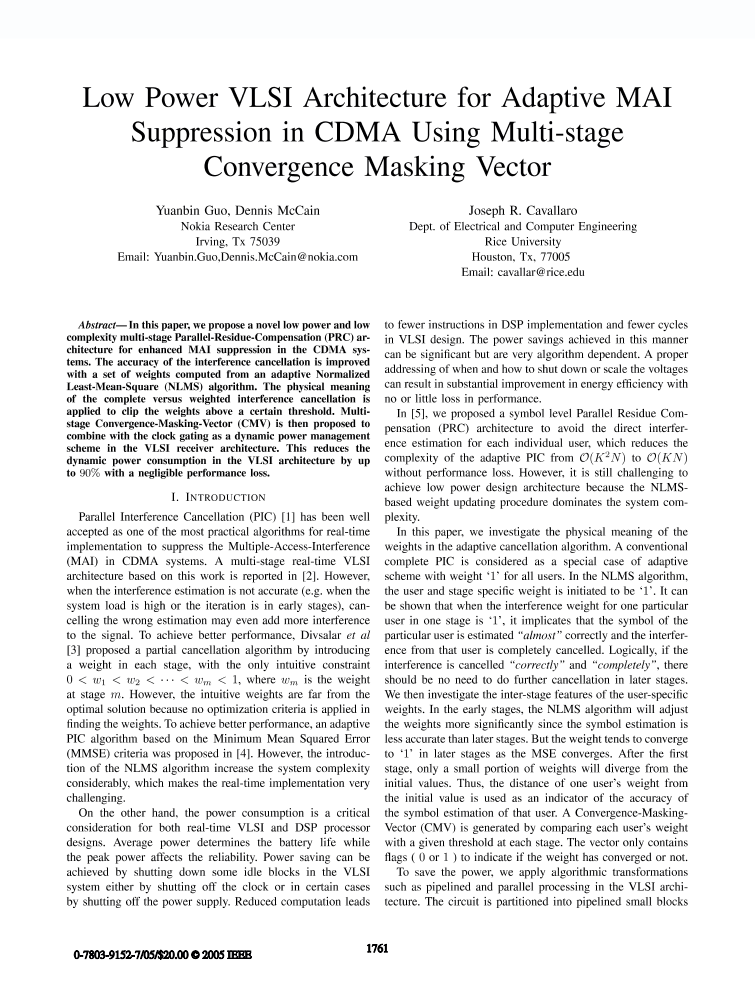

Low power VLSI architecture for adaptive MAI suppression in CDMA using multi-stage convergence masking vector | IEEE Conference Publication | IEEE Xplore

![PDF] Low Power Testing of VLSI Circuits Using Test Vector Reordering | Semantic Scholar PDF] Low Power Testing of VLSI Circuits Using Test Vector Reordering | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/d34c0238f5e6d7cf426c54ca6c09a7c6e1182805/4-TableV-1.png)

![PDF] Low Power Testing of VLSI Circuits Using Test Vector Reordering | Semantic Scholar PDF] Low Power Testing of VLSI Circuits Using Test Vector Reordering | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/d34c0238f5e6d7cf426c54ca6c09a7c6e1182805/3-TableI-1.png)